一块小小的芯片,如何实现百倍增长的计算能力?答案不在缩小的晶体管,而在颠覆性的封装技术。

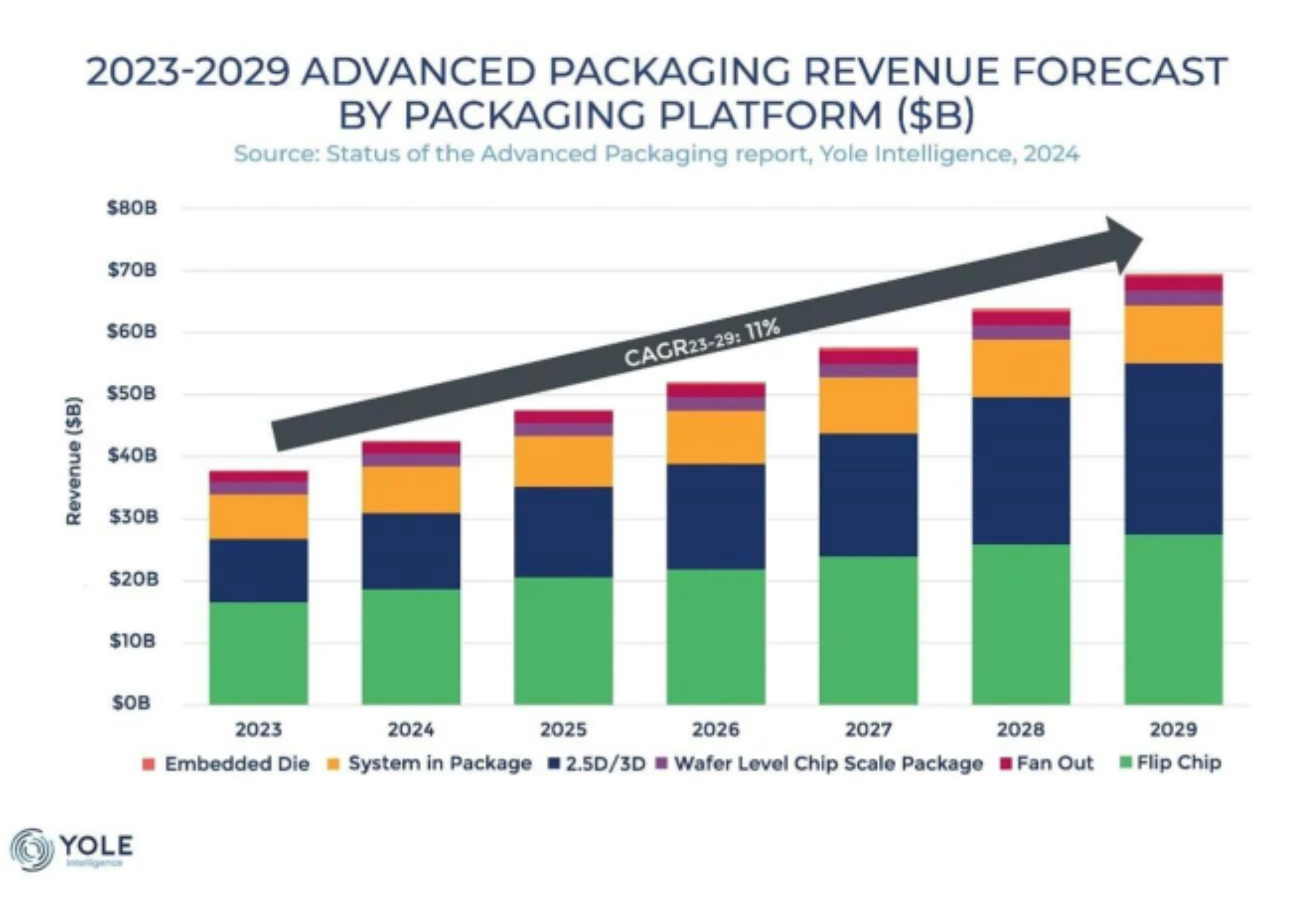

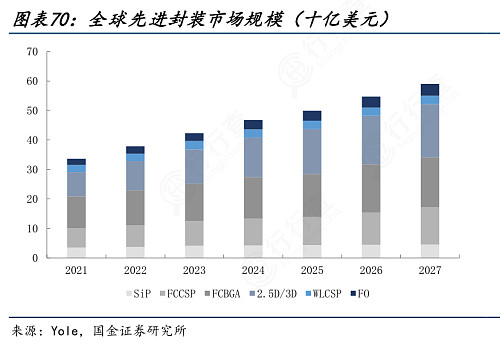

当 Yole Group 在《2025 先进封装产业报告》中抛出 460 亿美元的 2024 年市场规模数据时,整个半导体行业都感受到了这场革命的烈度 ——19% 的同比增幅远超消费市场的狂欢节奏,而 2030 年 794 亿美元的预测更意味着六年内将诞生一个 “封装界亚马逊”。驱动这场爆发的核心,正是 AI 与高性能计算掀起的 “模块化重构浪潮”。

01 市场暴涨,AI与高性能计算驱动增长

曾经仅应用于特定高端产品的先进封装技术,如今已成为消费电子大规模应用的关键技术,同时也为AR/VR、边缘AI、航空航天及国防等新兴市场提供关键支撑。

通信与基础设施领域2024至2030年间增长率达到14.9%,成为所有细分市场中增速最快的领域。

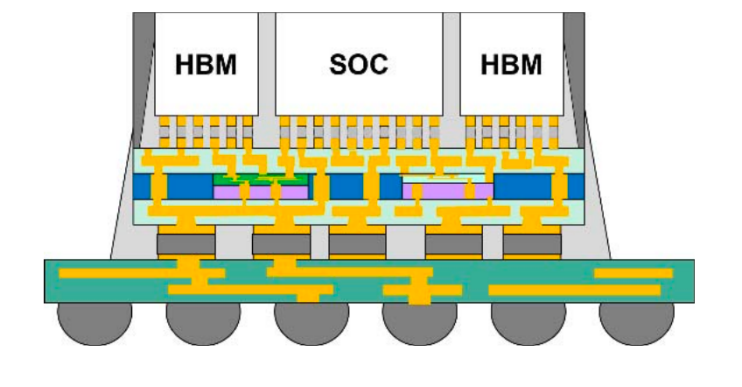

其背后动力包括AI加速器、GPU、云数据中心大规模建设,以及Chiplet架构的普及。随着系统复杂性提升,CoWoS、SoIC、EMIB、I-Cube及3D堆叠等先进封装技术,正成为高性能芯片集成的核心技术方案。

02 技术革新,从制程上探到系统下沉

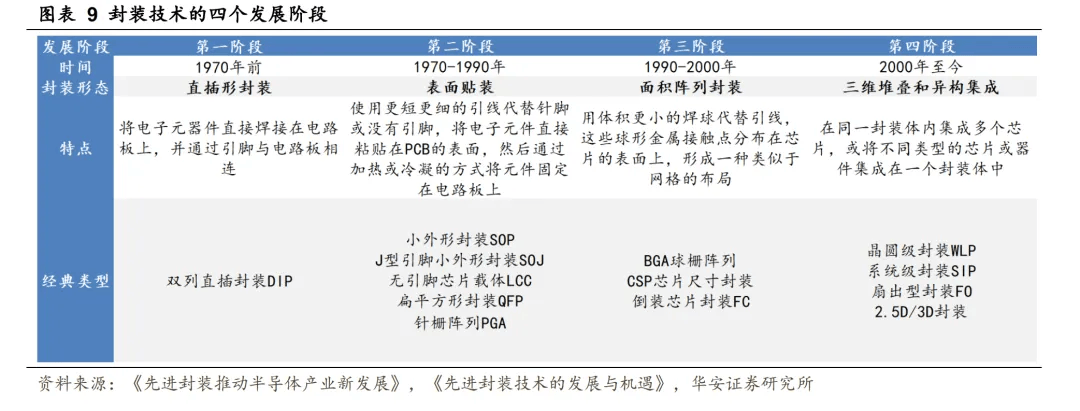

先进封装的技术发展方向主要朝两个方向演进。

一是制程上探,以单一功能芯片的高密度互联和电气性能优化为核心的同构集成结构。这方面技术包括晶圆级封装(WLP)、凸点工艺(Bumping)、硅通孔技术(TSV)和晶圆扇出技术(Fan-out)等。

二是系统下沉,以系统级封装(SiP)为代表,将原本分散贴装在PCB板上的多种功能芯片集成为一颗芯片,压缩模块体积、缩短电气连接距离以提升芯片系统功能,代表了侧重异构集成的发展方向。

系统级封装SiP的微小化优势显而易见。通过改变模组及缩小尺寸,为终端产品提供更大的电池空间,集成更多的功能;通过异质整合减少组装厂的工序,加上更高度自动化的工艺在前端集成,降低产业链复杂度。

03 Chiplet引领,颠覆传统芯片设计范式

随着芯片复杂性与制造成本提升,Chiplet架构逐渐成为异构集成和系统级平台化发展的关键方向。

Chiplet是在多芯片模组(MCM)基础上发展出的新型封装架构,将单一复杂芯片拆分为多个小型、独立且可复用的芯粒单元,并利用Flip-Chip、2.5D或3D等先进封装技术实现不同工艺、材料和功能芯片的灵活组合。

相比传统单芯片SoC方案,Chiplet方案在良率、性能和成本方面优势明显:小芯粒提升晶圆良率,降低生产风险;多芯片分布式架构满足高效能计算和扩展需求;异构芯片的灵活集成提升设计灵活性,有效控制成本。

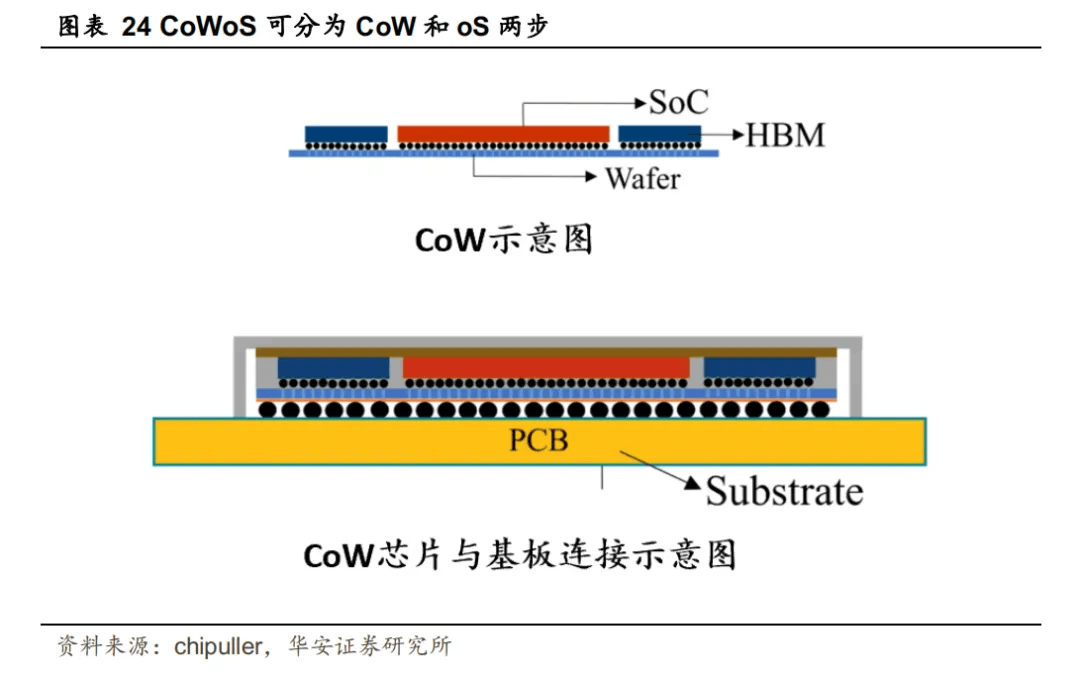

04 台积电CoWoS,打造“性能巨无霸”

台积电作为晶圆代工龙头,正开发一种全新的CoWoS-L封装技术,预计最早于明年推出。

该技术支持面积高达4,719平方毫米的中介层(约为光罩极限的5.5倍),并需要100×100mm的基板。可集成多达12个HBM4高带宽内存堆栈,相比现在可实现跨越式提升。

台积电预测,采用该技术制造的芯片将提供比当今领先设计高出三倍半的计算性能,有可能满足Nvidia Rubin GPU等即将推出的处理器的需求。

如此庞大的组件可以容纳四个3D堆叠集成芯片系统、十二个HBM4内存堆栈和多个I/O芯片,重新定义了高性能集成上限。

05 中国力量,国产先进封装加速突破

繁荣的背面往往藏着产业升级的“暗礁”——微米级的气泡缺陷,正成为制约封装良率和可靠性的“隐形杀手”。

屹立芯创致力于打造热流与气压的研发与应用平台,公司专精于先进封装制程气泡问题的解决,依托热流和气压两大核心技术,持续研发以多领域除泡系统(De-Void System)和晶圆级真空贴压膜系统(Wafer Vacuum Lamination System)为核心的两大产品系统与应用体系,提供多领域工艺制程中的气泡和压膜的整体解决方案。

目前,屹立芯创的智能除气泡系统与晶圆级真空贴压膜系统,已在多家国内封测龙头企业实现规模化稳定应用,并成功通过半导体制造、电子组装与汽车电子等领域头部客户的严格工艺验证。该系统广泛应用于半导体封装测试、人工智能芯片、机器人、新能源、汽车电子、5G通信及物联网等多个关键领域。

06 先进封装,从“辅助工序”到“性能引擎”

当全球先进封装市场向千亿美元的目标全速冲刺时,中国半导体装备产业也正实现从“解决有无”到“技术引领”的关键转变。这场围绕“微米级气泡”的工艺较量,看似是技术细节的优化,实则是产业话语权的争夺。

先进封装,已不再只是制造流程中的一环,而是成为驱动AI算力持续飞跃的“性能引擎”。它重新定义了芯片的可能性,也正在重塑全球半导体竞争的新格局。