在摩尔定律逐渐放缓的背景下,Chiplet(小芯片)技术和3D封装成为半导体行业突破性能与集成度瓶颈的

关键路径。然而,随着芯片集成度的提高,气泡缺陷成为影响封装良率的核心挑战之一。南京屹立芯创半导

体科技有限公司(ELEAD TECH)凭借其晶圆级真空贴压膜系统和多领域除泡系统,为先进封装提供了关键

解决方案,助力Chiplet与3D封装技术实现更高性能与可靠性。

1. Chiplet技术:模块化设计推动芯片创新

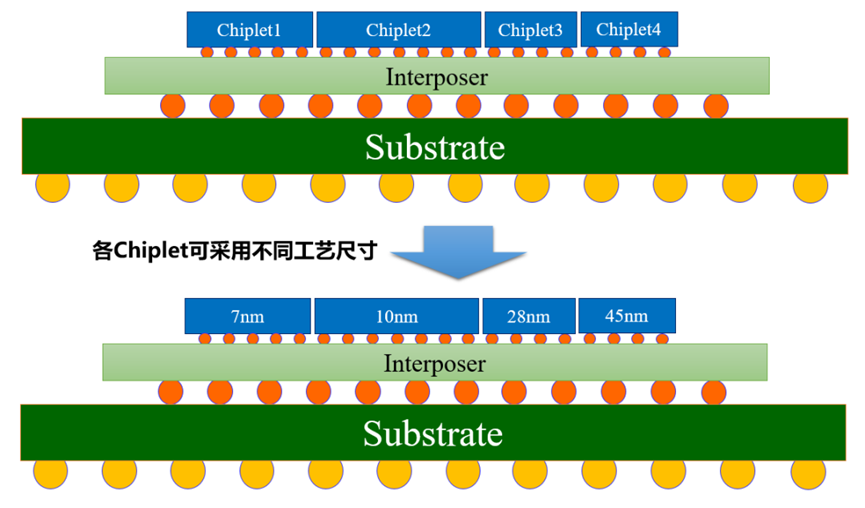

Chiplet技术将传统SoC(系统级芯片)拆解为多个独立功能模块(如计算单元、存储、I/O接口),通过先

进封装技术集成,类似“半导体乐高”。其优势包括:

灵活性:不同工艺节点的Chiplet可混合集成,例如CPU采用5nm工艺,而模拟电路采用成熟制程,降

低成本。

高性能:AMD的EPYC处理器采用Chiplet架构,通过3D堆叠实现更高带宽和能效。

良率优化:单个Chiplet良率更高,减少大尺寸单芯片的制造缺陷。

然而,Chiplet集成面临气泡残留问题,尤其是在底部填胶(Underfill)、芯片贴合(Die Attach)等工艺

中,气泡会导致散热不良、机械应力集中,甚至电路失效。

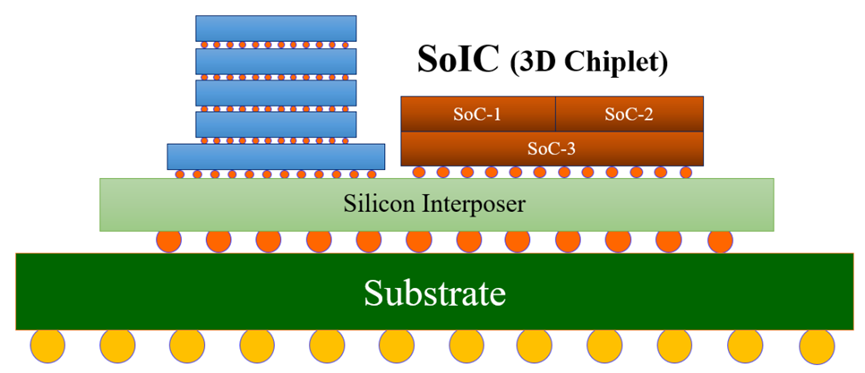

2. 3D封装:垂直堆叠突破性能极限

3D封装通过硅通孔(TSV)、混合键合(Hybrid Bonding)等技术,将Chiplet在垂直方向堆叠,显著提

升互连密度:

HBM(高带宽存储器):通过TSV实现存储与逻辑芯片的3D集成,带宽可达819GB/s,延迟降低80%。

异构集成:如NVIDIA Grace Hopper超级芯片,整合CPU与GPU裸片,优化AI计算效率。

但3D堆叠加剧了气泡问题,尤其是在高深宽比(>1:10)的TSV填孔和RDL(再布线层)工艺中,传统滚

轮压膜技术难以避免气泡残留。

3. 屹立芯创的解决方案:突破气泡瓶颈

屹立芯创专注于半导体先进封装中的气泡消除,其核心技术包括热流控制和气压调节,主要产品如下:

(1)晶圆级真空贴压膜系统(WVLA/WVLM/WVLS)

真空下贴膜+软垫气囊压合:区别于传统滚轮压膜,采用真空环境预铺设干膜,再通过弹性气囊震荡压合,

避免气泡残留,适用于凹凸晶圆表面(如Cu Pillar Bump)。

高深宽比填覆:支持1:20 TSV填孔,广泛应用于Flip Chip、Fan-out、3D-IC等制程。

智能自动化:兼容8"/12"晶圆,集成自动切割系统,提升生产效率。

(2)多领域除泡系统

真空压力交互切换:针对底部填胶、环氧树脂灌封等工艺,通过多段真空-压力循环消除气泡。

铟片散热方案:结合铟金属的高导热性,优化GPU/CPU封装散热,减少高温导致的气泡膨胀。

4. 行业应用与未来趋势

屹立芯创的技术已成功应用于:

AI/HPC芯片:如AMD MI300采用3D Chiplet集成,屹立芯创设备保障TSV填孔良率。

车用电子:自动驾驶芯片需要高可靠性封装,除泡技术提升长期稳定性。

5G/物联网:射频模块的异构集成依赖高精度贴膜与气泡控制。

随着玻璃通孔(TGV)、混合键合等技术的发展,屹立芯创的循环换热板专利技术(CN220062682U)将进一步优化3D封装的热管理能力。

Chiplet与3D封装正推动半导体行业进入“集成创新”时代,而气泡控制是确保良率的关键。屹立芯创凭借

真空贴压膜系统和智能除泡技术,成为全球除泡品类的领导者,为后摩尔时代的芯片性能突破提供核心支撑。

未来,随着标准化和跨行业协作的深化,Chiplet与3D封装将在AI、自动驾驶、高性能计算等领域持续释放

潜力。