2025年末的半导体圈,三条技术新闻勾勒出先进封装的“三国杀”格局:台积电CoWoS产能缺口扩大至15%,英伟达Blackwell芯片交货期被迫延长;AMD MI300凭借Chiplet+3D IC混合架构,在AI算力测试中追平英伟达;三星携SoP技术斩获特斯拉165亿美元订单,试图弯道超车。从CoWoS的产能垄断到Chiplet的快速普及,再到3D IC的垂直突破,这场看似混乱的技术混战,实则是产业对性能极限、成本控制、供应链安全的深层博弈。拨开技术迷雾,我们能看到这场“路线之争”的四大核心命题。

一、争“性能天花板”:谁能突破算力与带宽的物理极限?

先进封装的本质是解决“芯片性能提升瓶颈”,当7nm以下制程逼近物理极限时,三种技术路线从不同维度冲击性能天花板,但核心诉求高度一致:实现更高算力、更大带宽与更低延迟。

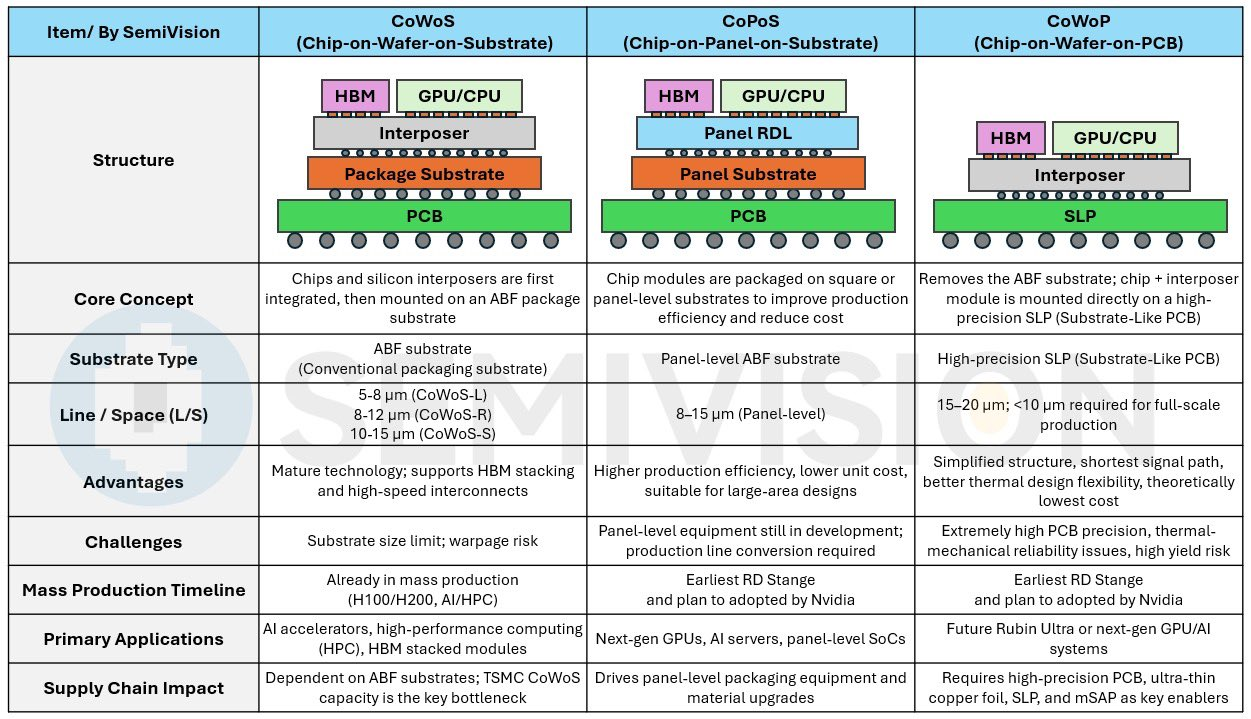

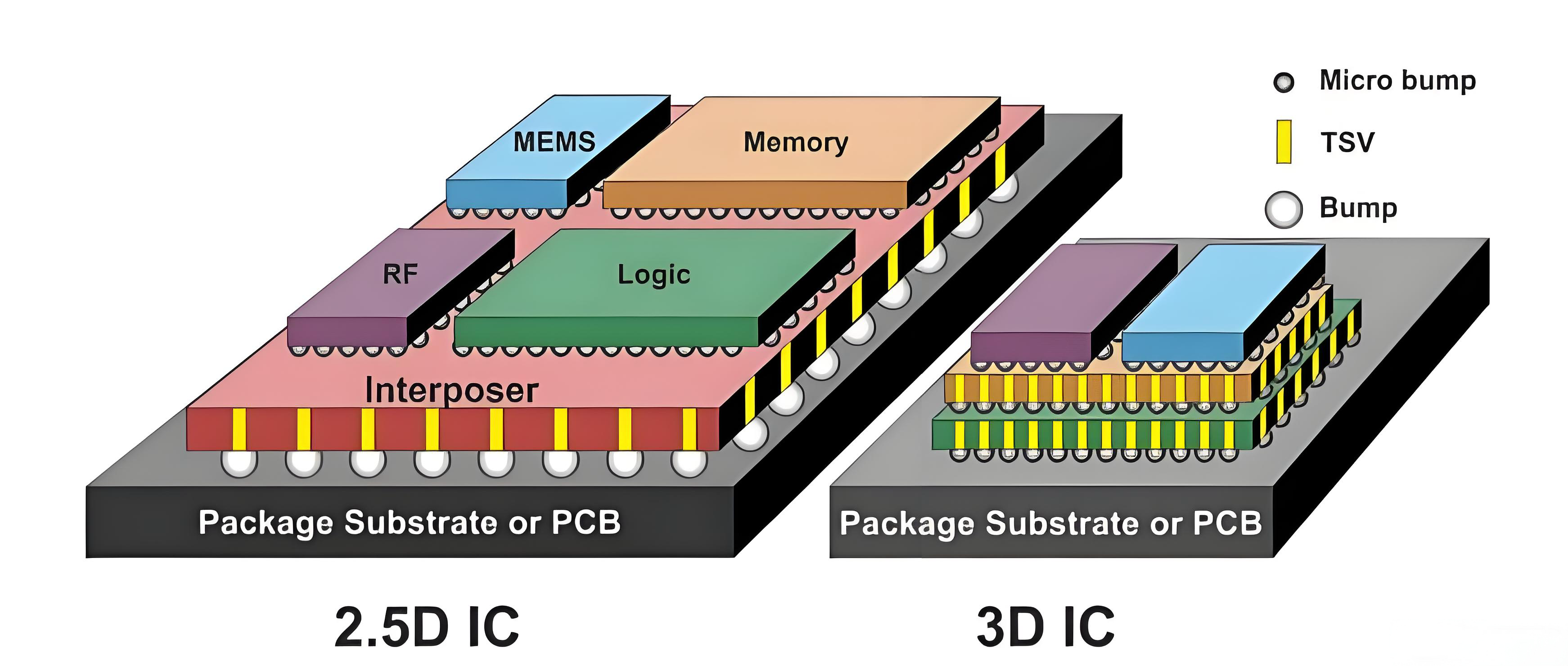

CoWoS以“豪华中介”姿态占据高端性能制高点。作为台积电主导的2.5D封装技术,其核心创新是通过硅中介层实现逻辑芯片与HBM内存的高密度互联,如同为芯片搭建“超高速桥梁”。最新的CoWoS-S5技术已将中介层面积拓展至2400mm²,支持8颗HBM3内存与2颗SoC芯片集成,内存带宽高达5.3TB/s,这也是英伟达H100、AMD MI300等顶级AI芯片首选该技术的核心原因。但性能优势背后是严苛的物理限制:大尺寸硅中介层的热密度集中问题突出,当HBM堆叠数量超过6层时,局部温度可能突破120℃,必须配套定制化散热方案。

图片引用SemiVision

3D IC则以“垂直堆叠”思路突破空间限制。通过硅通孔(TSV)或混合键合技术,将多颗芯片垂直叠加,使互联距离从微米级缩短至纳米级,功耗降低40%以上。三星的X-Cube技术是典型代表,其铜-铜混合键合方案已推进至4微米以下超精细连接规格,实现12层HBM内存垂直堆叠的SAINT-D技术,彻底摆脱了对硅中介层的依赖。英特尔的Foveros技术同样表现亮眼,其数据中心GPU Max系列通过3D堆叠集成超过千亿个晶体管,在同等功耗下算力较传统封装提升2.2倍。不过3D IC的性能提升受限于键合良率,当堆叠层数超过8层时,良率可能从90%骤降至65%,成为性能突破的隐性门槛。

Chiplet则以“异构集成”重构性能组合逻辑。通过将大芯片拆分为多个功能芯粒(如算力芯粒、存储芯粒、I/O芯粒),采用不同制程工艺制造后再通过封装互联,实现“按需组合”的性能优化。AMD MI300的成功极具代表性,其采用“台积电SoIC 3D封装+CoWoS 2.5D封装”的混合架构,将5nm算力芯粒与28nm I/O芯粒集成,在实现1.2TB内存带宽的同时,研发成本降低30%。UCIe 2.0标准的发布更让Chiplet如虎添翼,支持64通道收发配置与800Gbps带宽传输,使跨厂商芯粒互操作成为可能。但Chiplet的性能短板也很明显,芯粒间的互联延迟仍高于单芯片架构,在对实时性要求极高的自动驾驶场景中仍需谨慎应用。

二、争“成本性价比”:如何平衡研发投入与量产经济性?

如果说性能是技术路线的“上限”,成本就是决定其商业化生命力的“底线”。三种技术在成本结构上的巨大差异,使其形成了清晰的场景分层,也造就了当前“高端选CoWoS、量产选Chiplet、存储选3D IC”的格局。

CoWoS的“性能溢价”背后是高昂的成本代价。硅中介层的制造需要前道高深宽比刻蚀设备,占封装BOM成本的50%-70%,部分高端芯片甚至出现“封装成本超过芯片本体”的极端情况。2025年台积电CoWoS工艺涨价15%-20%,进一步推高了终端产品成本。但对于AI训练、HPC等高端场景,这种成本是“必要投入”——英伟达H100采用CoWoS封装后,算力较前代提升3倍,客户愿意为性能溢价买单,这也是台积电CoWoS产能即便缺口15%仍供不应求的核心原因。

Chiplet则以“降本利器”姿态颠覆行业认知。其核心成本优势来自“制程混搭”:仅将核心算力芯粒采用5nm等先进制程,外围辅助芯粒采用28nm等成熟制程,使整体研发成本降低40%以上。通富微电的数据显示,采用Chiplet技术后,3nm芯片良率从40%提升至85%,4nm芯片良率更是高达99.2%,进一步摊薄了单位成本。这种成本优势使其在消费电子、工业控制等量产场景快速普及,2025年国内Chiplet相关订单增速已超过50%。但Chiplet的成本控制依赖标准化,若缺乏UCIe等统一协议,定制化互联设计可能使成本反超传统封装。

3D IC的成本逻辑聚焦“存储密度提升”。在存储芯片领域,3D堆叠技术通过垂直拓展空间,使单位面积存储容量提升10倍以上,单位成本降低60%。三星的12层HBM堆叠方案,正是通过3D IC技术将存储带宽提升至1TB/s,同时使单GB成本较传统方案降低25%。但在逻辑芯片领域,3D IC的成本优势并不明显:混合键合设备单价超过2000万美元,且良率随堆叠层数增加而显著下降,目前仅在高端服务器芯片中少量应用。

三、争“产能与供应链安全”:谁能掌控量产主动权?

当技术成熟度达到临界点后,产能布局与供应链稳定性成为决定技术路线胜负的关键。当前三种技术的产能格局呈现“CoWoS垄断、Chiplet分散、3D IC突围”的特征,供应链安全诉求正深刻影响企业的路线选择。

CoWoS面临“产能垄断与缺口并存”的困境。台积电目前掌控全球90%以上的CoWoS产能,2025年产能约100万片,2026年预计仅提升至105-110万片,而英伟达一家就预订了2026年60%的产能,用于Blackwell和Rubin芯片生产,导致谷歌、Meta等客户面临“排队周期超过产品生命周期”的被动局面。这种产能垄断使供应链风险凸显,2025年因台积电高雄工厂设备调试延迟,全球AI芯片交付量减少15%,直接推动苹果、高通等企业加速评估替代方案。三星虽推出对标CoWoS的I-Cube S技术,但良率仅为台积电的70%,短期内难以形成有效替代。

Chiplet凭借“产能分散化”优势成为供应链安全的“缓冲器”。与CoWoS集中于台积电不同,Chiplet可适配长电科技、通富微电等多家厂商的产能,长电科技的XDFOI技术已实现102mm×102mm超大尺寸封装,支持4nm节点产品稳定出货。这种分散产能布局,使企业可通过“主供+备用”策略降低风险,比如AMD同时与台积电、通富微电合作Chiplet封装,确保产能安全。更重要的是,Chiplet对封装基板等材料的兼容性更强,国内企业在封装基板领域的突破(如清河电科实现8μm线路精度量产),进一步提升了供应链自主可控性。

3D IC则在存储领域构建了相对安全的供应链。三星、美光等存储巨头已实现3D堆叠技术的自主量产,国内长江存储的Xtacking 3.0技术也实现8层堆叠量产,良率达85%以上。但在逻辑芯片3D封装领域,混合键合设备仍依赖应用材料、东京电子等海外厂商,国内长川科技虽推出国产设备,但市场份额不足5%,供应链安全仍存隐患。

四、争“生态主导权”:谁能定义行业标准与合作规则?

技术路线的终极竞争是生态的竞争。当前台积电、英特尔、三星三大巨头正通过“技术平台+标准制定+客户绑定”构建生态壁垒,而CoWoS、3D IC、Chiplet的路线之争,本质是三大生态体系的话语权博弈。

台积电以CoWoS为核心构建“3DFabric生态”。通过整合CoWoS(2.5D)、SoIC(3D)、InFO等技术,形成覆盖从消费电子到AI/HPC全场景的封装平台,英伟达、AMD、博通等头部芯片设计企业均深度绑定该平台。台积电的生态优势体现在“设计-制造-封装”的协同:其为客户提供从芯片设计仿真到封装量产的全流程服务,使客户切换成本极高。为巩固优势,台积电还联合产业链推出CoWoS-L技术,通过硅桥+RDL中介层的混合架构,解决大尺寸硅中介层良率问题,进一步提升生态粘性。

英特尔以“EMIB+Foveros”组合打造“本土生态”。EMIB技术通过嵌入式硅桥设计降低成本,适合定制ASIC场景;Foveros技术实现3D垂直堆叠,两者结合形成差异化优势。英特尔的生态策略聚焦“供应链本土化”,其在美国新墨西哥州、俄亥俄州建设先进封装基地,为苹果、高通等客户提供“本土设计-本土制造-本土封装”的全链条服务,精准契合美国政府的供应链安全诉求。近期苹果、高通密集招聘EMIB技术人才,标志着英特尔生态正从本土走向全球。

三星以“I-Cube+X-Cube”体系图谋“存储-逻辑协同生态”。凭借在HBM存储领域的优势,三星通过“存储芯片+先进封装”的捆绑策略吸引客户,特斯拉165亿美元AI芯片订单即包含HBM与3D封装的配套服务。三星的差异化突破点在于SoP技术,采用415mm×510mm超大尺寸面板作为封装载体,省去PCB和硅中介层,成本较CoWoS降低30%,试图通过技术创新重构生态规则。

Chiplet则凭借UCIe标准形成“开放生态”。UCIe 2.0标准支持高达64通道配置与800Gbps带宽,兼容CoWoS、EMIB等多种封装技术,已吸引英特尔、AMD、台积电等70多家企业加入。这种开放生态使中小芯片设计企业无需依赖单一巨头,通过组合不同厂商的芯粒即可实现高端芯片设计,为行业带来新的可能性。

五、国内突围:在混战中寻找差异化机会

面对全球巨头的生态壁垒,国内企业正通过“聚焦Chiplet、突破3D IC、追赶CoWoS”的策略实现突围。长电科技的XDFOI Chiplet技术已实现4nm节点量产,102mm×102mm超大尺寸封装技术达到业界领先水平;通富微电的3nm Chiplet良率突破85%,获得英伟达、AMD认证;在CoWoS领域,通富微电通过大尺寸多芯片封装技术升级,良率提升至95%以上,逐步实现进口替代。

国内企业的核心机会在于“场景定制化”:在汽车电子、工业互联网等细分场景,通过Chiplet技术为客户提供定制化封装方案,避开与巨头在高端CoWoS领域的直接竞争。同时,国内在硅中介层、热管理材料等领域的专利申请量已占全球42%,为技术反超奠定基础。

回望这场技术路线之争,我们会发现没有“最优解”,只有“最适配的选择”:AI训练选CoWoS追求极致性能,消费电子选Chiplet平衡成本与规模,存储芯片选3D IC提升密度——三种技术并非替代关系,而是正在走向融合。台积电的3DFabric、英特尔的混合架构、三星的协同方案,本质都是“2.5D+3D+Chiplet”的异构集成。未来,谁能更好地整合三种技术的优势,谁就能在先进封装的终极竞争中胜出。而对于行业从业者而言,看懂这场博弈的核心逻辑,才能在技术选择与战略布局中抢占先机。