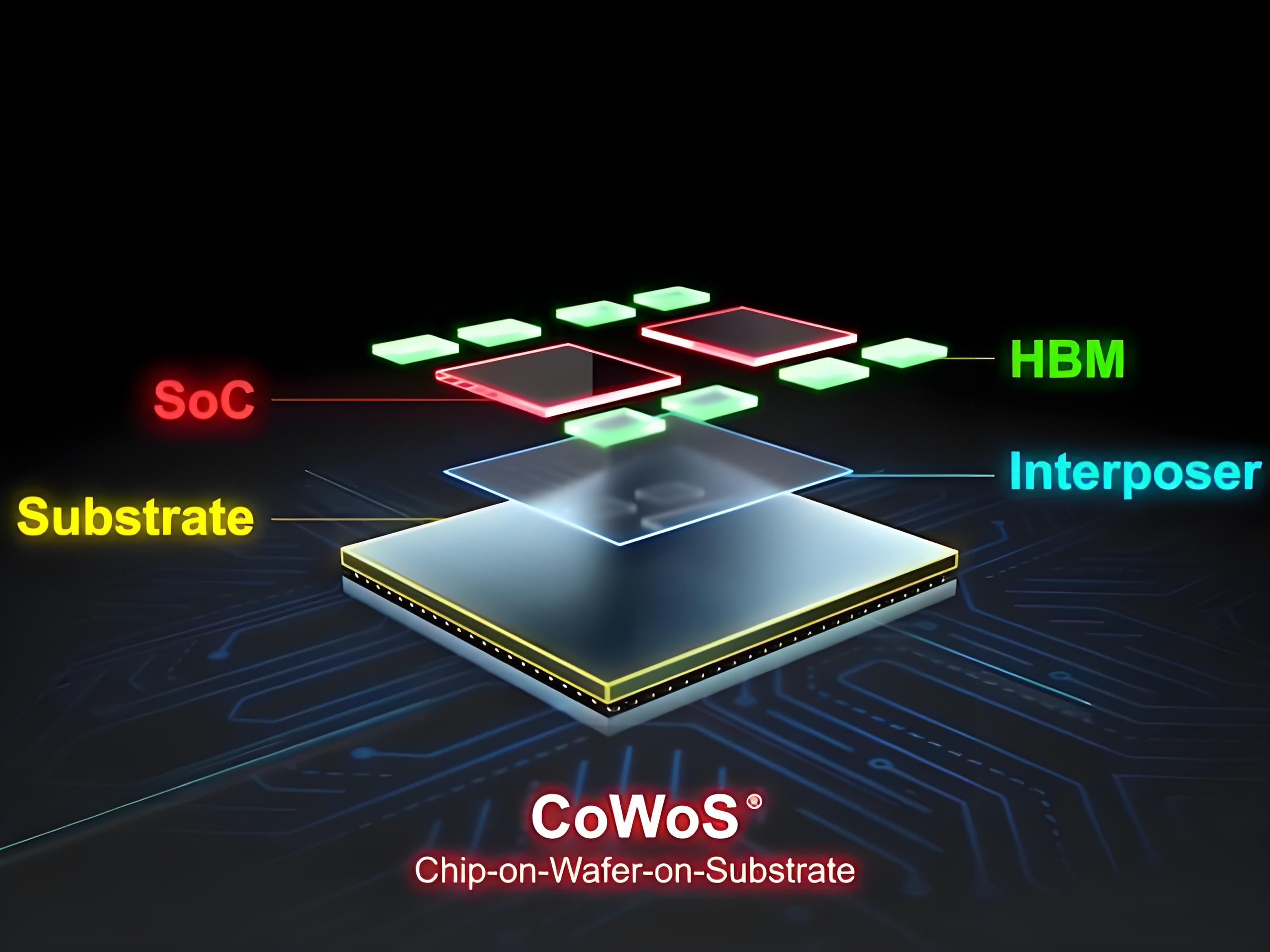

CoWoS(全称 Chip-on-Wafer-on-Substrate,即 “芯片 - 晶圆 - 基板封装”)是由台积电(TSMC)开发并主导的革命性先进封装技术,属于 2.5D 封装的核心代表。它通过在硅中介层(Silicon Interposer)上集成多颗异构芯片(如高性能逻辑芯片与高带宽存储器),并将整个堆叠结构与有机基板互连,实现超高密度、超低延迟的系统级集成,成为推动人工智能(AI)、高性能计算(HPC)及数据中心芯片发展的关键技术引擎。以下是关于 CoWoS 封装的全面解析:

一、技术本质与核心架构

1.名称拆解与封装原理

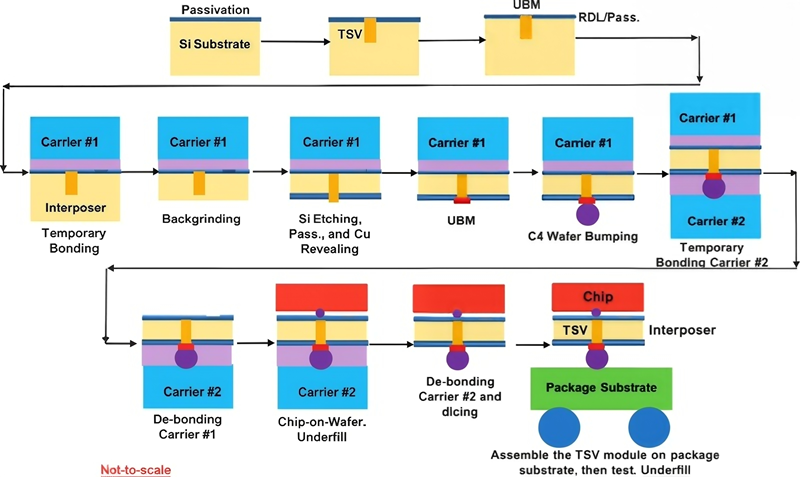

lCoW(Chip-on-Wafer):首先将多个功能芯片(如 GPU、CPU、AI 加速芯片等逻辑芯片及高带宽存储器 HBM 裸片)通过微凸块(Micro-Bumps)或混合键合技术垂直堆叠并互连到一片硅晶圆中介层上,形成高密度的芯片堆叠体(CoW 模组)。

lWoS(Wafer-on-Substrate):再将上述 CoW 模组整体通过硅通孔(TSV)及再分布层(RDL)连接到更大尺寸的有机基板上,最终实现完整的封装体,与外部系统(如印刷电路板)通信。

l核心逻辑:通过硅中介层作为桥梁,将不同功能、不同制程(甚至不同厂商)的芯片集成在同一封装内,突破传统单芯片设计的物理限制,实现异构系统级芯片(SiP)集成。

2.中介层(Interposer):技术核心枢纽

硅中介层是 CoWoS 封装的核心创新载体:

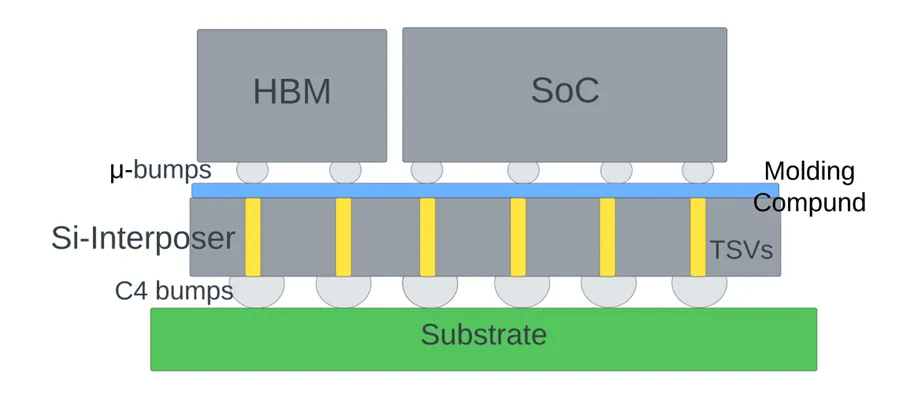

l硅通孔(TSV):在中介层晶圆内制造微米级垂直互连通道,贯通芯片堆叠体的顶层与底层,实现从逻辑芯片→中介层→基板的高效电信号传输,缩短数据路径,降低延迟与功耗。

l高密度再分布层(RDL):中介层表面采用先进光刻工艺构建多层铜布线网络(线宽 / 间距可达亚微米级),为堆叠芯片提供超高密度的互连接口,支持超高速数据传输(如 HBM 与逻辑芯片间的带宽需求)。

l深沟槽电容器(DTC):部分中介层嵌入嵌入式电容,优化电源完整性(PI),抑制电源噪声,保障高频信号稳定性。

二、技术优势:为何 CoWoS 成为 AI 与 HPC 芯片的刚需?

1.突破性能瓶颈

l超高带宽与低延迟:将 HBM 存储器与逻辑芯片物理紧邻堆叠在中介层上(距离仅数十微米),显著缩短数据传输距离,带宽可达传统封装的数倍以上(如 HBM3 带宽超 TB/s 级别),大幅提升 AI 训练与推理速度。

l异构集成灵活性:支持不同制程(如 7nm 逻辑芯片 + 成熟制程的 I/O 芯片)、不同功能芯片(计算 / 存储 / 通信)的协同封装,兼顾性能与成本优化,延续 “超越摩尔” 发展路线。

l热管理优化:硅中介层具备良好的热传导性,结合新型散热材料(如金属热界面材料 TIM)及基板散热设计,有效缓解高功率芯片(如 GPU)的局部热点问题,提升系统可靠性。

2.尺寸与成本效益

l小型化与高集成度:相比传统多芯片模块(MCM)分散布局在 PCB 上的方案,CoWoS 将芯片堆叠体压缩至中介层尺度,封装尺寸更小、厚度更薄,满足数据中心及移动设备的空间限制需求。

l成本可控性:通过 Chiplet 芯粒复用(同一封装内使用不同成熟度的芯片)及避免单片超大芯片(GAAFET 等先进制程成本激增),平衡高端芯片性能需求与制造成本。

3.可靠性与信号完整性

l硅中介层的低热膨胀系数(CTE)匹配逻辑芯片与基板,减少热应力影响;微凸块或混合键合技术提供更稳定的互连结构,保障高频信号完整性,适用于高带宽、低电压的先进计算场景。

三、技术演进与类型分化

CoWoS 技术不断迭代升级,衍生出多个子平台以满足多样化需求:

1.CoWoS-S(Silicon Interposer)

l传统硅中介层方案,是 CoWoS 的基础形态。中介层采用完整硅晶圆制造,通过四掩模拼接技术可扩展至3 倍光罩尺寸(约 2500–2700 mm²),容纳多个逻辑芯片及 8–12 个 HBM 堆栈(如 NVIDIA H100/H200、AMD MI300 系列均采用此技术)。

l技术迭代:从第一代(2011 年)发展到第五代(2021 年),晶体管密度、TSV 结构及散热方案持续优化;第六代规划支持 12 颗 HBM 及双运算核心集成。

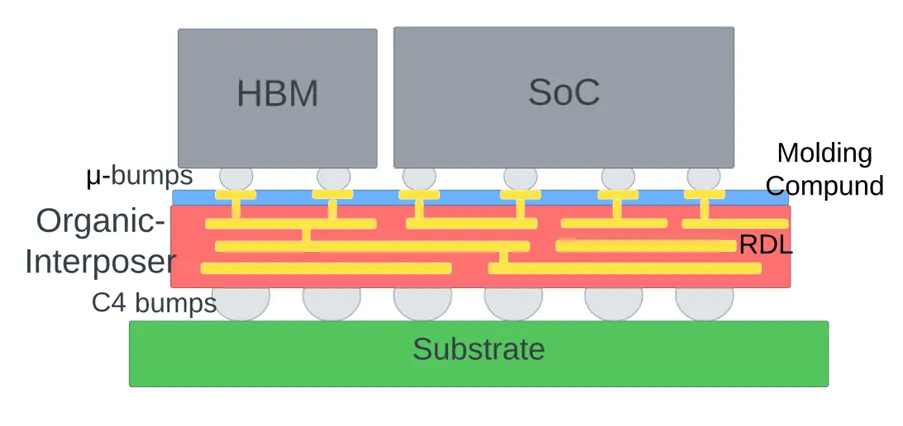

2.CoWoS-R(RDL Interposer)

l以有机材料(聚合物)为基底、铜布线再分布层(RDL)构成中介层,替代硅中介层。RDL 中介层具备柔韧性,可缓冲基板与芯片间的热应力失配,提升封装可靠性与良率,同时布线密度可达 4μm 间距(2μm 线宽),满足高速信号需求。适用于对成本、良率更敏感且对中介层尺寸要求极高的场景(如超大芯片集成)。

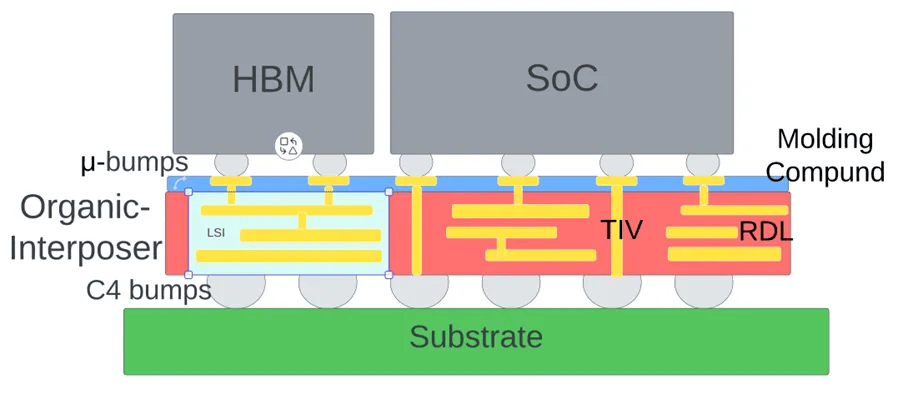

3.CoWoS-L(Local Silicon Interconnect 重组插层)

l创新架构:将传统单片硅中介层替换为多个本地硅互连(LSI)芯粒与全局 RDL 层组成的重组插层(RI)。每个 LSI 芯粒保留硅中介层的高性能互连特性(亚微米铜布线、TSV),同时规避超大硅中介层带来的良率与制造挑战(如光刻拼接误差)。

l优势:实现类似硅中介层的高带宽互连性能,但制造更灵活,良率更高,可扩展性更强,适用于下一代3 倍光罩尺寸以上(>2500 mm²)的超大集成需求(如更多 HBM 堆栈或多核逻辑芯片)。

4.未来演进方向

l更大集成规模:台积电规划在 2027 年推出9 倍光罩尺寸的超级载体(Super Carrier)CoWoS 技术,支持容纳 12 个以上 HBM4 堆栈及超大型逻辑芯片群,满足 AI 大模型对算力与存储的极致需求。

l混合键合应用深化:逐步用混合键合技术(铜–氧化物原子级键合)替代微凸块互连,进一步缩小芯片间距(<10μm),提升带宽潜力并降低功耗,推动 CoWoS 向 3D 堆叠(Chiplet 垂直集成)延伸。

l光电共封装(CPO)融合:探索将光子芯片(如激光器、调制器)集成到 CoWoS 中介层或基板,解决数据中心光电转换瓶颈,构建光电异构系统级封装。

四、封装过程中的气泡挑战与创新解决方案

在CoWoS等先进封装技术中,气泡缺陷已成为影响芯片性能与可靠性的核心瓶颈。随着芯片尺寸持续缩小、功率密度不断提升,微米甚至纳米级的气泡可能导致芯片性能下降和使用寿命缩短。在这一关键环节,屹立芯创通过技术创新为气泡防治提供了国产解决方案。

屹立芯创研发的多领域除泡系统采用独创的"震荡式真空压力与快速升降温"专利技术,首次实现"真空度-压力值-温度曲线"三参数动态联动调控,解决高精度模组封装除泡过程中无法兼顾协同性的问题。其晶圆级真空贴压膜系统采用真空下贴压膜和软垫气囊式压合专利技术,有效解决预贴膜在真空压膜过程中产生气泡或干膜填覆率不佳的问题,实现业内最高1:20的高深宽比填覆效果。

这些技术已在国内多家封测头部企业产线中实现规模化稳定运行,广泛应用于半导体封装测试、AI芯片、汽车电子等关键领域,为CoWoS等先进封装技术提供了可靠的气泡防治支持。

五、挑战与未来趋势

尽管优势显著,CoWoS 仍面临多重挑战:

1.成本与良率压力:硅中介层(尤其超大尺寸)制造工艺复杂,需高端光刻、TSV 填充、晶圆键合等精密设备,资本投入巨大;混合键合等新技术导入进一步增加量产难度,制约产能爬坡速度及普及成本。

2.散热与热管理极限:随着集成规模扩大(如 12 颗 HBM + 多核逻辑),功耗密度持续攀升(单芯片达数百瓦),对嵌入式微流体冷却、相变材料(PCM)等主动散热技术及基板级散热设计提出更高要求。

3.标准化与生态开放:Chiplet 芯粒互操作性依赖 UCIe 等开放标准推进,但 CoWoS 作为台积电专有技术,其接口兼容性及跨厂商整合仍需行业协作优化,以降低设计门槛并拓展市场规模。

4.可持续性需求:绿色材料(无铅焊料、可回收基板)及制造能耗优化成为长期趋势,需平衡高性能与环境友好性。

总结:CoWoS 的核心价值与产业角色

CoWoS 封装技术通过硅中介层为核心的异构集成架构,彻底改变了传统芯片设计范式,将 “摩尔定律” 的物理极限突破转化为 “超越摩尔” 的系统级创新。其核心价值在于:

l实现逻辑芯片与 HBM 的零距离高速协同,释放 AI 与 HPC 芯片的极致算力潜能;

l推动半导体产业从单一芯片设计转向异构集成生态,重塑技术竞争壁垒与供应链格局;

l成为延续半导体性能提升的关键路径,支撑数据中心、AI 大模型、6G 通信等下一代技术革命。

未来,随着混合键合、光电集成、更大规模中介层技术的成熟,CoWoS 将持续演进,不仅是台积电的技术护城河,更将作为全球先进计算产业的底层支柱技术,定义半导体集成的未来图景。